#### Introduction:

- Single sample mode

- Sampling frequency which is set at 44.1 kHz

- Successive data samples/ Double sample mode

- Dataload signal is provided as a start conversion signal.

- 8-bit input data buffer.

- Built-in High speed processor.

- Single Power Supply: +5V

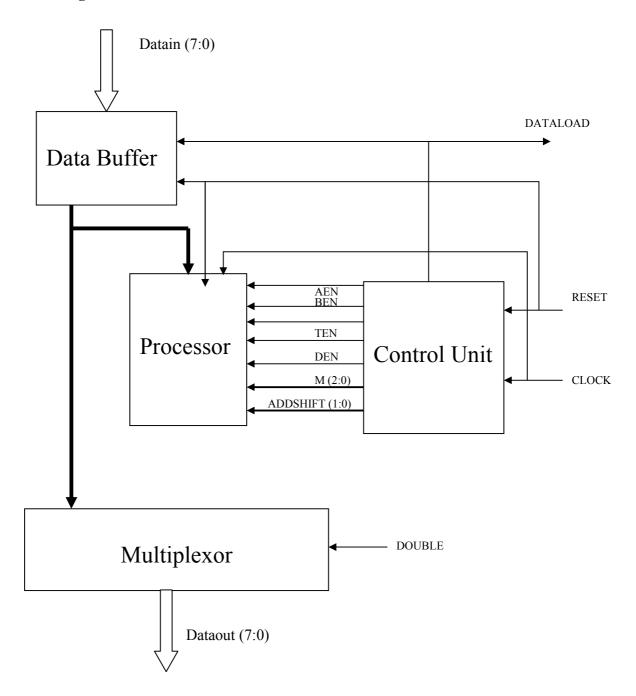

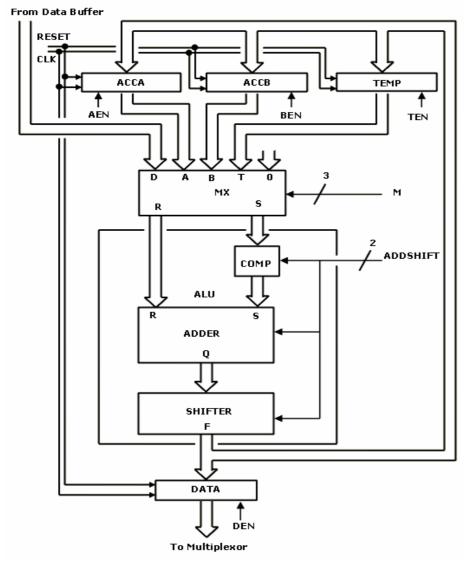

LDI86 is 8-bit linear interpolator. Linear interpolation is a common technique used in the processing of digital audio and video data. Consecutive data samples are analysed and intermediate values computed to improve sound quality or enhance video imagery. The following block diagram details an 8-bit data interpolator suitable for doubling the number of samples in an audio system.

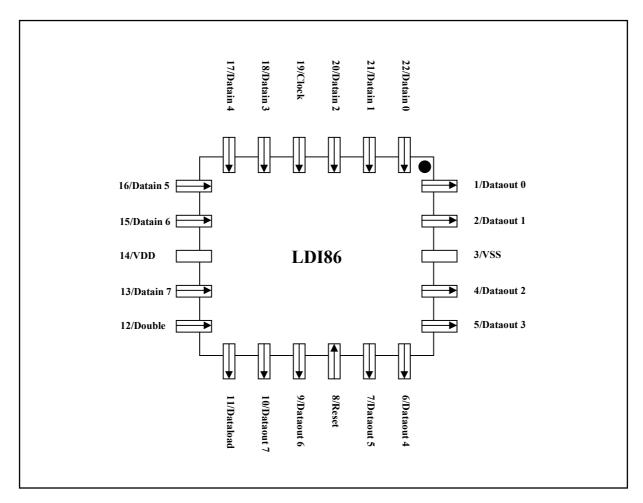

### Pin Configuration:

# **Block Diagram:**

# **Pin Description**:

| Symbol    | I/O                                                                                                                                                                                | Description                                                                                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dataout 0 | O                                                                                                                                                                                  | Output Data 0                                                                                                                                                                                                     |

| Dataout 1 | O                                                                                                                                                                                  | Output Data 1                                                                                                                                                                                                     |

| VSS       | P                                                                                                                                                                                  | Ground                                                                                                                                                                                                            |

| Dataout 2 | O                                                                                                                                                                                  | Output Data 2                                                                                                                                                                                                     |

| Dataout 3 | O                                                                                                                                                                                  | Output Data 3                                                                                                                                                                                                     |

| Dataout 4 | O                                                                                                                                                                                  | Output Data 4                                                                                                                                                                                                     |

| Dataout 5 | О                                                                                                                                                                                  | Output Data 5                                                                                                                                                                                                     |

| Reset     | I                                                                                                                                                                                  | Active low System Reset                                                                                                                                                                                           |

| Dataout 6 | O                                                                                                                                                                                  | Output Data 6                                                                                                                                                                                                     |

| Dataout 7 | O                                                                                                                                                                                  | Output Data 7                                                                                                                                                                                                     |

| Dataload  | O                                                                                                                                                                                  | Synchronises the External device                                                                                                                                                                                  |

| Double    | I                                                                                                                                                                                  | Selecting the Single or Double mode                                                                                                                                                                               |

| Datain 7  | I                                                                                                                                                                                  | Input Data 7                                                                                                                                                                                                      |

| VDD       | P                                                                                                                                                                                  | Supply Voltage                                                                                                                                                                                                    |

| Datain 6  | I                                                                                                                                                                                  | Input Data 6                                                                                                                                                                                                      |

| Datain 5  | I                                                                                                                                                                                  | Input Data 5                                                                                                                                                                                                      |

| Datain 4  | I                                                                                                                                                                                  | Input Data 4                                                                                                                                                                                                      |

| Datain 3  | I                                                                                                                                                                                  | Input Data 3                                                                                                                                                                                                      |

| Clock     | I                                                                                                                                                                                  | System Clock                                                                                                                                                                                                      |

| Datain 2  | I                                                                                                                                                                                  | Input Data 2                                                                                                                                                                                                      |

| Datain 1  | I                                                                                                                                                                                  | Input Data 1                                                                                                                                                                                                      |

| Datain 0  | I                                                                                                                                                                                  | Input Data 0                                                                                                                                                                                                      |

|           | Dataout 0 Dataout 1 VSS Dataout 2 Dataout 3 Dataout 4 Dataout 5 Reset Dataout 6 Dataout 7 Dataload Double Datain 7 VDD Datain 6 Datain 5 Datain 4 Datain 3 Clock Datain 2 Datain 1 | Dataout 0 O Dataout 1 O VSS P Dataout 2 O Dataout 3 O Dataout 4 O Dataout 5 O Reset I Dataout 6 O Dataout 7 O Dataload O Double I Datain 7 I VDD P Datain 6 I Datain 5 I Datain 4 I Datain 3 I Clock I Datain 1 I |

**Technology: MIETEC 2u** Chip Area: 244mm X 244mm

## ABSOLUTE MAXIMUM RATINGS

| Characteristic        | Symbol      | MIN  | MAX            | Unit |

|-----------------------|-------------|------|----------------|------|

| Supply Voltage        | $V_{ m DD}$ | -0.5 | 7.5            | V    |

| Low Voltage           |             | -0.5 | 7.5            | V    |

| High Voltage          |             | -0.5 | 12.5           | V    |

| Input Voltage         | Vı          | -0.5 | $V_{DD} + 0.5$ | V    |

| Output Voltage        | Vo          | -0.5 | 7.5            | V    |

| Operating Temperature | Topr        | -55  | 125            | °C   |

| Storage Temperature   | Tstg        | -65  | 150            | °C   |

## OPERATING CONDITIONS

| Characteristic | Symbol      | MIN | MAX | Unit |

|----------------|-------------|-----|-----|------|

| Supply Voltage | $V_{ m DD}$ | 3   | 7   | V    |

| Low Voltage    |             | 3   | 7   | V    |

| High Voltage   |             | 7   | 12  | V    |

### ELECTRICAL CHARACTERISTICS

### DC Characteristics

( $V_{DD} = 5V$ ,  $V_{SS} = 0V$ ,  $T_a = 25$ °C, unless otherwise specified)

| Characteristic      | Symbol          | Conditions                 | Min  | Тур | Max  | Unit |

|---------------------|-----------------|----------------------------|------|-----|------|------|

| High Input Voltage  | V <sub>IH</sub> |                            | 3.5  |     | 5.5  | V    |

| Low Input Voltage   | VIL             |                            | -0.5 |     | 1.5  | V    |

| High Output Voltage | Voh             | $(I_{OL} < 1 \text{mA})$   | 4.95 |     |      | V    |

| Low Output Voltage  | Vol             | $(I_{OH} \le 1 \text{mA})$ |      |     | 0.05 | V    |

| Input Capacitance   | Cin             |                            |      |     | 10   | pF   |

| Iol                 | Iol             | $V_{OUT} = 0.4$            | 3.2  |     |      | mA   |

| Іон                 | Іон             | $V_{OUT} = 4.6$            | 1.6  |     |      | mA   |

| Ios                 | Ios             | Source                     | -40  |     |      | mA   |

|                     | Ios             | Sink                       | 74   |     |      | mA   |

## AC Characteristics

( $V_{DD} = 5V$ ,  $V_{SS} = 0V$ ,  $T_a = 25$ °C, unless otherwise specified)

| Characteristic        | Symbol | Min | Тур | Max | Unit |

|-----------------------|--------|-----|-----|-----|------|

| Rising & Falling Time | tr, tf |     |     |     |      |

| Clock Frequency       | fск    |     |     |     |      |

| Setup Time            | tsu    |     |     |     |      |

| Hold Time             | tн     |     |     |     |      |

| Delay Time            | to     |     |     |     |      |

#### Functional Description:

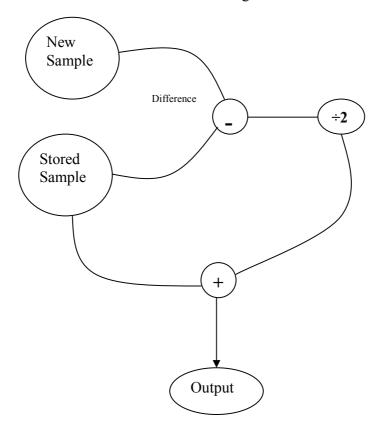

Linear interpolation is a common technique used in the processing of digital audio and video data. Linear interpolation allows predicting an unknown value, if any two particular values are know and assume that the rate of change is constant.

The Processor takes each sample in turn, computes the difference between it and the previous value, divides this difference by 2 and adds to the previous value to form a new intermediate value.

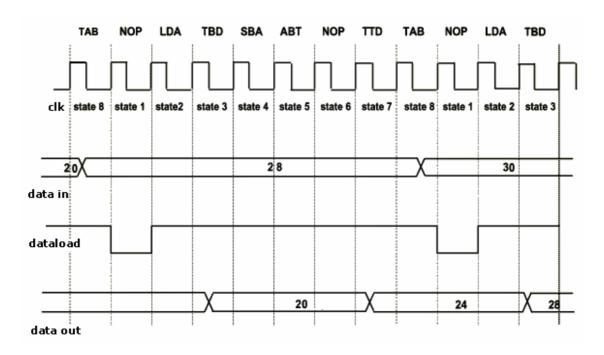

The free running system Clock operates at 8 times the sample frequency thereby allowing the control unit eight clock cycles between samples to issue the required computational instructions. The Dataload signal synchronises the arrival of new data with the start of the next computational cycle. This signal is also provided as a chip output to act as a Start Conversion signal to an external analogue to digital converter during testing of the manufactured device.

Samples comprising alternate original and intermediate values are output at twice the sampling frequency.

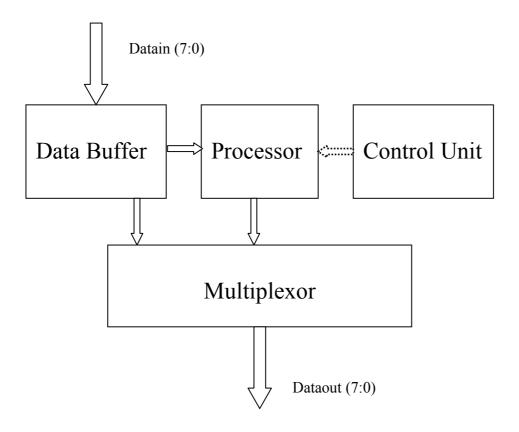

The following block diagram details the data flow. Information to be sampled is first buffered and transferred to processor and multiplexor. The computed data from processor is fed to multiplexor. Depends upon the requirement by Double signal, a data can be selected to pass it to output pins.

Data Flow Diagram:

An active LOW system Reset is also provided to initialise the control unit and to clear the processor and data buffer registers for simulation and device testing.

LDI86 is divided into following four major blocks.

- 1. Data Buffer

- 2. Processor

- 3. Control Unit

- 4. Multiplexor

- 1. Data Buffer: It is an 8-bit positive edged triggered register. Internally Dataload is used as a clock to sample the data. This sampling frequency is set to 44.1 kHz. An active LOW system Reset is provided internally, to initialize the buffer with set value.

#### 2. Processor:

LDI86 contain an 8-bit RISC processor. Processor is high speed mathematical operator. It can perform addition, subtraction, multiplication (x 2) and divider ( $\div$  2). Processor compromises the multiplexor, 8-bit adder, 8-bit shifter, Complimentor, and 8-bit registers. Every unit in processor is driven by Control unit.

## 3. Control Unit:

Control unit is the heart of the LDI86. It is design with 8-state finite state machine. Eight different states are sequenced to control the processor of LDI86.

| will the states are sequenced to consider the processor of 22 fee. |     |     |     |     |     |     |     |     |

|--------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| STATE                                                              | NOP | LDA | TBD | SBA | ABT | NOP | TTD | TAB |

| SIGNAL                                                             |     |     |     |     |     |     |     |     |

| M(2:0)                                                             | 110 | 100 | 011 | 000 | 001 | 110 | 101 | 010 |

| ADDSHIFT(1:0)                                                      | 01  | 01  | 01  | 10  | 01  | 01  | 01  | 01  |

| AEN                                                                |     | 1   | 0   | 0   | 0   |     | 0   | 0   |

| BEN                                                                |     | 0   | 0   | 0   | 0   |     | 0   | 1   |

| TEN                                                                |     | 0   | 0   | 1   | 1   |     | 0   | 0   |

| DEN                                                                |     | 0   | 1   | 0   | 0   |     | 1   | 0   |

| DATALOAD                                                           | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

Dataload is generated on every new sample cycle.

4. Multiplexor: It is a two channel, 8-bit multiplxor with Double as input. Whether the user wants single sample or double sample mode, it can be chose from double signal.

### Glossary

Linear interpolation: The simplest kind of automatic inbetweening is linear inbetweening which is done with a mathematical process of guessing intermediate locations called linear interpolation. To interpolate simple means to calculate a new value inbetween two known values. Linear interpolation creates new values at equal distances along a line between two known values.